သတ်မှတ်ချက်

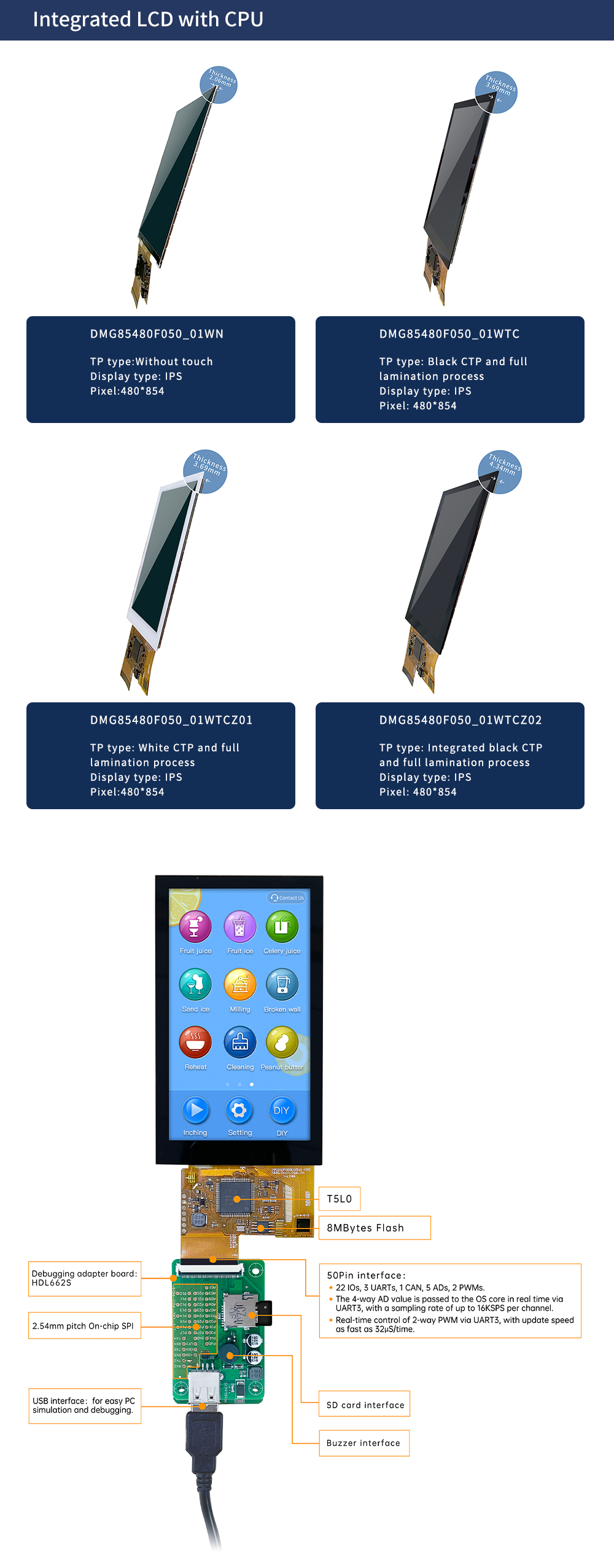

| T5L0 ASIC | T5L0 ASIC သည် ပါဝါနည်းပါးပြီး ကုန်ကျစရိတ်သက်သာသော GUI နှင့် 2020 ခုနှစ်တွင် ထုတ်လုပ်သည့် အသေးစား LCD နှင့် အစုလိုက်အပြုံလိုက်အတွက် DWIN Technology မှ ဒီဇိုင်းထုတ်ထားသော single-chip dual-core ASIC မြင့်မားစွာပေါင်းစပ်ထားသော အပလီကေးရှင်းတစ်ခုဖြစ်သည်။ | ||

| အရောင် | 262K အရောင်များ | ||

| LCD အမျိုးအစား | IPS-TFT-LCD၊ | ||

| ရှုထောင့် | မြင်ကွင်းကျယ်သော နတ်သမီး၊ ပုံမှန်တန်ဖိုး 85°/85°/85°/85°(L/R/U/D) | ||

| ဆုံးဖြတ်ချက် | 480×854 | ||

| နောက်ခံအလင်း | အယ်လ်အီးဒီ | ||

| တောက်ပမှု | DMG85480F050_01WN:400nit DMG85480F050_01WTC:350nit DMG85480F050_01WTCZ01:350nit DMG85480F050_01WTCZ02:100nit | ||

| ရိုက်ပါ။ | CTP (capacitive touch panel) | ||

| ဖွဲ့စည်းပုံ | G+G ဖွဲ့စည်းပုံ | ||

| ထိမုဒ် | ထောက်ပံကို တို့ထိပြီး ဆွဲယူပါ။ | ||

| Surface Hardness | 6H | ||

| အလင်းပို့လွှတ်ခြင်း။ | 90% ကျော် | ||

| ဘဝ | အကြိမ် 1,000,000 ကျော်ထိတယ်။ | ||

| ပါဝါဗို့အား | 3.6~5.5V၊ ပုံမှန်တန်ဖိုး 5V | ||

| လည်ပတ်မှုလက်ရှိ | VCC=5V၊ အများဆုံး နောက်ခံအလင်း၊ 300mA | ||

| VCC=5V၊ နောက်ခံအလင်းပိတ်၊ 95mA | |||

| အလုပ်အပူချိန် | -10 ℃ ~ 60 ℃ | ||

| သိုလှောင်မှုအပူချိန် | -20 ℃ ~ 70 ℃ | ||

| စိုထိုင်းဆ အလုပ်လုပ်ခြင်း။ | 10% ~ 90% RH၊ ပုံမှန်တန်ဖိုး 60% RH | ||

| အသုံးပြုသူ အင်တာဖေ့စ် | 50Pin_0.5mm FPC | ||

| Baudrate | 3150~3225600bps | ||

| အထွက်ဗို့အား | အထွက် 1;3.0~3.3 V | ||

| အထွက် 0;0~0.3 V | |||

| Input Voltage (RXD) | အဝင် 1;3.3V | ||

| အဝင် 0;0~0.5V | |||

| အင်တာဖေ့စ် | UART2: TTL; UART4- TTL; (OS ဖွဲ့စည်းမှုပုံစံပြီးနောက်သာ ရနိုင်သည်) UART5- TTL; (OS ပြင်ဆင်သတ်မှတ်ပြီးနောက်သာ ရနိုင်သည်။ | ||

| ဒေတာပုံစံ | UART2: N81; UART4- N81/E81/O81/N82;4 မုဒ်များ (OS ဖွဲ့စည်းမှုပုံစံ) UART5- N81/E81/O81/N82;4 မုဒ်များ (OS ဖွဲ့စည်းမှုပုံစံ) | ||

| တံ | အဓိပ္ပါယ် | I/O | Functional Description |

| 1 | 5V | I | ပါဝါထောက်ပံ့မှု၊ DC3.6-5.5V |

| 2 | 5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 ADCs ထည့်သွင်းပါ။3.3V ပါဝါထောက်ပံ့မှုတွင် 12-bit ရုပ်ထွက်။0-3.3V အဝင်ဗို့အား။AD6 မှလွဲ၍ ကျန်ဒေတာများကို 16KHz နမူနာနှုန်းဖြင့် အချိန်နှင့်တပြေးညီ UART3 မှတစ်ဆင့် OS core သို့ ပေးပို့ပါသည်။AD1 နှင့် AD5 ကို အပြိုင်အသုံးပြုနိုင်ပြီး AD3 နှင့် AD7 ကို အပြိုင်အသုံးပြုနိုင်ပြီး 32KHz နမူနာ AD နှစ်ခုနှင့် ညီမျှသည်။AD1၊ AD3၊ AD5၊ AD7 ကို 64KHz နမူနာ AD နှင့် ညီမျှသော အပြိုင်သုံးနိုင်သည်။နမူနာယူခြင်းဖြင့် 64Hz 16bit AD တန်ဖိုးကို ရယူရန် ဒေတာကို 1024 ကြိမ် ပေါင်းပြီး 64 ဖြင့် ပိုင်းခြားထားသည်။ |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD1 | I | |

| 11 | +3.3 | O | 3.3V အထွက်၊ အမြင့်ဆုံးဝန် 150mA။ |

| 12 | SPK | O | buzzer သို့မဟုတ် စပီကာကို မောင်းနှင်ရန် ပြင်ပ MOSFET။ပါဝါဖွင့်မှုအဆင့်နိမ့်ကြောင်းသေချာစေရန် ပြင်ပ 10K ခုခံအားကို မြေပေါ်ဆွဲချသင့်သည်။ |

| 13 | SD_CD | I/O | SD/SDHC အင်တာဖေ့စ်၊ SD_CK သည် SD ကတ်အင်တာဖေ့စ်အနီးရှိ 22pF capacitor ကို GND သို့ ချိတ်ဆက်သည်။ |

| 14 | SD_CK | O | |

| 15 | SD_D3 | I/O | |

| 16 | SD_D2 | I/O | |

| 17 | SD_D1 | I/O | |

| 18 | SD_D0 | I/O | |

| 19 | PWM0 | O | 2 16-bit PWM အထွက်။ပါဝါဖွင့်မှုအဆင့်နိမ့်ကြောင်းသေချာစေရန် ပြင်ပ 10K ခုခံအားကို မြေပေါ်ဆွဲချသင့်သည်။OS core ကို UART3 မှတစ်ဆင့် အချိန်နှင့်တပြေးညီ ထိန်းချုပ်နိုင်သည်။ |

| 20 | PWM1 | O | |

| 21 | P3.3 | I/O | IO နှစ်ခုလုံးသို့ချိတ်ဆက်ရန် RX8130 သို့မဟုတ် SD2058 I2C RTC ကိုအသုံးပြုပါက SCL သည် P3.2 သို့ချိတ်ဆက်သင့်ပြီး SDA သည် 10K resistor 3.3V အထိအပြိုင် P3.3 သို့ချိတ်ဆက်သင့်သည်။ |

| 22 | P3.2 | I/O | |

| 23 | P3.1/EX1 | I/O | ၎င်းကို တစ်ချိန်တည်းတွင် ပြင်ပအနှောက်အယှက်ဖြစ်စေသည့် 1 ထည့်သွင်းမှုအဖြစ် အသုံးပြုနိုင်ပြီး ဗို့အားနိမ့်အဆင့် သို့မဟုတ် နောက်မှလိုက်နေသော အစွန်းပိုင်းကြားဖြတ်မုဒ်နှစ်ခုလုံးကို ပံ့ပိုးပေးသည်။ |

| 24 | P3.0/EX0 | I/O | ၎င်းကို တစ်ချိန်တည်းတွင် ပြင်ပအနှောက်အယှက်ဖြစ်စေသည့် 0 ထည့်သွင်းမှုအဖြစ် အသုံးပြုနိုင်ပြီး ဗို့အားနိမ့်အဆင့် သို့မဟုတ် နောက်လိုက်နေသော အစွန်းပိုင်းကြားဖြတ်မုဒ်နှစ်ခုလုံးကို ပံ့ပိုးပေးသည်။ |

| 25 | P2.7 | I/O | IO အင်တာဖေ့စ် |

| 26 | P2.6 | I/O | IO အင်တာဖေ့စ် |

| 27 | P2.5 | I/O | IO အင်တာဖေ့စ် |

| 28 | P2.4 | I/O | IO အင်တာဖေ့စ် |

| 29 | P2.3 | I/O | IO အင်တာဖေ့စ် |

| 30 | P2.2 | I/O | IO အင်တာဖေ့စ် |

| 31 | P2.1 | I/O | IO အင်တာဖေ့စ် |

| 32 | P2.0 | I/O | IO အင်တာဖေ့စ် |

| 33 | P1.7 | I/O | IO အင်တာဖေ့စ် |

| 34 | P1.6 | I/O | IO အင်တာဖေ့စ် |

| 35 | P1.5 | I/O | IO အင်တာဖေ့စ် |

| 36 | P1.4 | I/O | IO အင်တာဖေ့စ် |

| 37 | P1.3 | I/O | IO အင်တာဖေ့စ် |

| 38 | P1.2 | I/O | IO အင်တာဖေ့စ် |

| 39 | P1.1 | I/O | IO အင်တာဖေ့စ် |

| 40 | P1.0 | I/O | IO အင်တာဖေ့စ် |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | I/O | IO အင်တာဖေ့စ် |

| 46 | P0.1 | I/O | IO အင်တာဖေ့စ် |

| 47 | CAN_TX | O | အင်တာဖေ့စ်လုပ်နိုင်သည်။ |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (OS Core ၏ UART2 အမှတ်စဉ် ဆိပ်ကမ်း) |

| 50 | UART2_RXD | I |