—— DWIN Froum မှမျှဝေသည်။

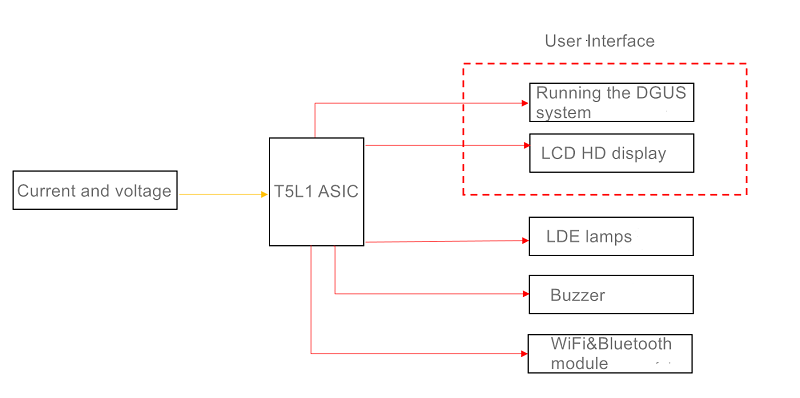

စက်တစ်ခုလုံး၏ ထိန်းချုပ်မှုဗဟိုအဖြစ် DWIN T5L1 ချစ်ပ်ကို အသုံးပြု၍ ထိတွေ့မှု၊ ADC ရယူမှု၊ PWM ထိန်းချုပ်မှု အချက်အလက်များကို လက်ခံရယူပြီး လက်ရှိအခြေအနေကို အချိန်နှင့်တပြေးညီ ပြသရန် 3.5 လက်မ LCD မျက်နှာပြင်ကို မောင်းနှင်စေသည်။WiFi module မှတဆင့် LED အလင်းရင်းမြစ်တောက်ပမှုကို အဝေးထိန်းထိချိန်ညှိမှုကို ပံ့ပိုးပေးပြီး အသံနှိုးစက်ကို ပံ့ပိုးပေးသည်။

ပရိုဂရမ်အင်္ဂါရပ်များ-

1. မြင့်မားသောကြိမ်နှုန်းဖြင့်လည်ပတ်ရန် T5L ချစ်ပ်ကိုအသုံးပြုပါ၊ AD analog နမူနာသည် တည်ငြိမ်သည်၊ အမှားသည် သေးငယ်သည်။

2. အမှားရှာပြင်ခြင်းနှင့် ပရိုဂရမ်မီးလောင်ခြင်းအတွက် PC နှင့် တိုက်ရိုက်ချိတ်ဆက်ထားသော TYPE C ကို ပံ့ပိုးပါ။

3. မြန်နှုန်းမြင့် OS core interface၊ 16bit parallel port ကို ပံ့ပိုးပါ။UI core PWM ပို့တ်၊ AD ပေါက်သည် ထွက်လာသည်၊ ကုန်ကျစရိတ်နည်းသော လျှောက်လွှာဒီဇိုင်း၊ အပို MCU ထည့်ရန် မလိုအပ်ပါ။

4. WiFi၊ Bluetooth အဝေးထိန်းခလုတ်ကို ပံ့ပိုးပါ။

5. 5~12V DC ကျယ်ပြန့်ဗို့အားနှင့် ကျယ်ပြန့်သောထည့်သွင်းမှုကို ပံ့ပိုးပေးသည်။

1.1 အစီအစဥ်ဇယား

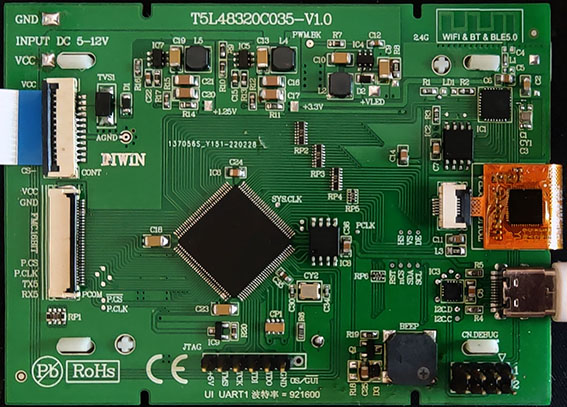

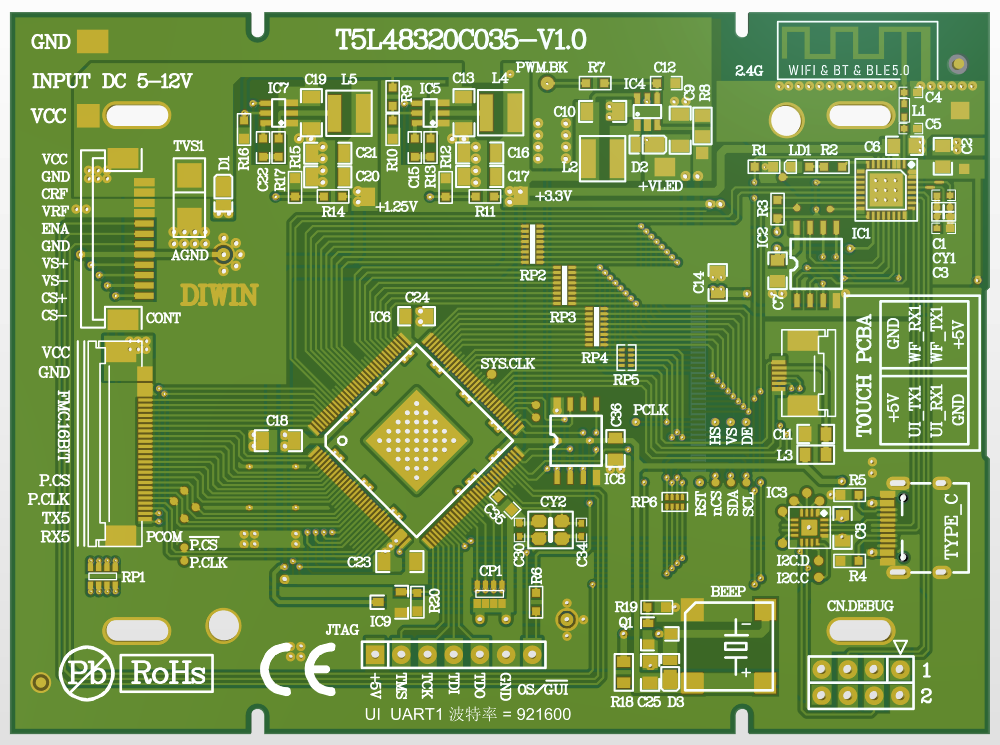

1.2 PCB ဘုတ်အဖွဲ့

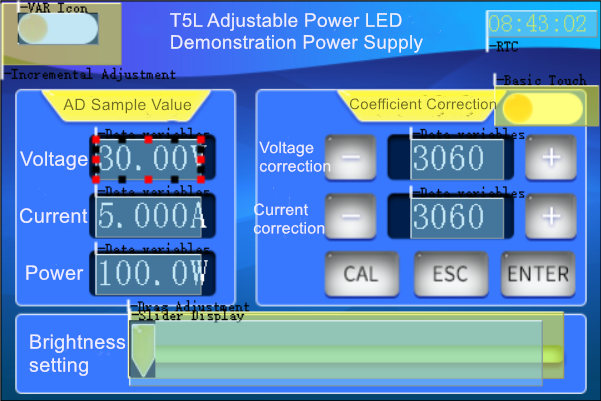

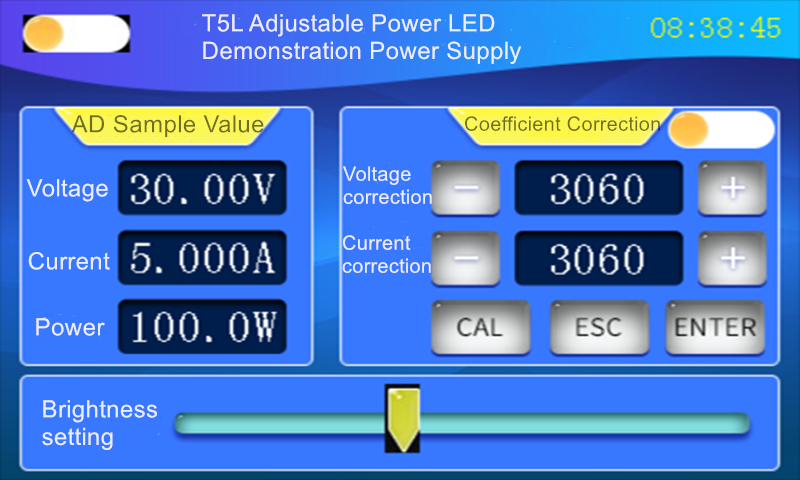

1.3 အသုံးပြုသူ အင်တာဖေ့စ်

ရှက်ဖွယ်နိဒါန်း-

(၁) ဟာ့ဒ်ဝဲ ဆားကစ် ဒီဇိုင်း

1.4 T5L48320C035 ဆားကစ်ပုံ

1. MCU logic power supply 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. MCU core power supply 1.25V: C23, C24;

3. MCU analog power supply 3.3V: C35 သည် MCU အတွက် analog power supply ဖြစ်သည်။စာစီစာရိုက်သတ်မှတ်သည့်အခါ၊ core 1.25V မြေပြင်နှင့် logic ground ကို အတူတကွပေါင်းစပ်နိုင်သော်လည်း analog ground ကို ခွဲခြားထားရပါမည်။Analog ground နှင့် digital ground ကို LDO output အကြီးစား capacitor ၏ negative pole တွင် စုဆောင်းသင့်ပြီး analog positive pole ကို LDO large capacitor ၏ positive pole တွင် စုဆောင်းထားသင့်သည်၊ သို့မှသာ AD sampling Noise ကို နည်းပါးအောင် ပြုလုပ်နိုင်မည်ဖြစ်သည်။

4. AD analog signal acquisition circuit- CP1 သည် AD analog input filter capacitor ဖြစ်သည်။နမူနာယူခြင်းအမှားကို လျှော့ချရန်အတွက် MCU ၏ analog ground နှင့် digital ground ကို သီးခြားခွဲထားသည်။CP1 ၏ အနုတ်လက္ခဏာဝင်ရိုးအား အနည်းဆုံး impedance ဖြင့် MCU ၏ analog ground နှင့် ချိတ်ဆက်ထားရမည်ဖြစ်ပြီး crystal oscillator ၏ parallel capacitors နှစ်ခုကို MCU ၏ analog ground နှင့် ချိတ်ဆက်ထားသည်။

5. Buzzer circuit- C25 သည် buzzer အတွက် power supply capacitor ဖြစ်သည်။buzzer သည် inductive device တစ်ခုဖြစ်ပြီး လည်ပတ်နေစဉ်အတွင်း အထွတ်အထိပ် လျှပ်စီးကြောင်း ရှိလာမည်ဖြစ်သည်။အထွတ်အထိပ်ကို လျှော့ချရန်အတွက် MOS tube သည် linear region တွင်အလုပ်လုပ်စေရန်နှင့် switch mode တွင်အလုပ်လုပ်စေရန် circuit ကို design လုပ်ရန် buzzer ၏ MOS drive current ကို လျှော့ချရန်လိုအပ်ပါသည်။Buzzer ၏အသံအရည်အသွေးကိုချိန်ညှိရန်နှင့် buzzer အသံကြည်လင်ပြတ်သားပြီးသာယာစေရန်အတွက် R18 ကို buzzer ၏အစွန်းနှစ်ဖက်တွင်အပြိုင်ချိတ်ဆက်သင့်သည်။

6. WiFi ဆားကစ်- WiFi+Bluetooth+BLE ဖြင့် ESP32-C နမူနာယူထားသော WiFi ချစ်ပ်။ဝိုင်ယာကြိုးပေါ်တွင် RF ပါဝါမြေနှင့် အချက်ပြမြေကို ခွဲခြားထားသည်။

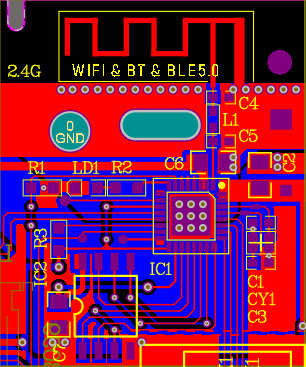

1.5 WiFi ဆားကစ် ဒီဇိုင်း

အထက်ပါပုံတွင်၊ ကြေးနီအလွှာ၏အပေါ်ပိုင်းသည် power ground loop ဖြစ်သည်။WiFi အင်တင်နာ ရောင်ပြန်ဟပ်မှု မြေပြင်ကွင်းပတ်သည် ပါဝါမြေပြင်သို့ ကြီးမားသော ဧရိယာရှိရမည်ဖြစ်ပြီး ပါဝါမြေပြင်၏ စုစည်းမှုအမှတ်မှာ C6 ၏ အနုတ်မှတ်တိုင်ဖြစ်သည်။ပါဝါမြေပြင်နှင့် WiFi အင်တင်နာကြားတွင် ရောင်ပြန်ဟပ်နေသော လျှပ်စီးကြောင်းကို ပံ့ပိုးပေးရမည်ဖြစ်သောကြောင့် WiFi အင်တင်နာအောက်တွင် ကြေးနီအကာအရံရှိရပါမည်။ကြေးနီအလွှာ၏ အရှည်သည် WiFi အင်တင်နာ၏ တိုးချဲ့မှု အရှည်ထက် ကျော်လွန်ပြီး တိုးချဲ့မှုသည် WiFi ၏ အာရုံခံနိုင်စွမ်းကို တိုးစေမည်ဖြစ်သည်။C2 ၏ အနှုတ်ဝင်ရိုးစွန်းတွင် အမှတ်။ကြေးနီ၏ကြီးမားသောဧရိယာသည် WiFi အင်တင်နာရောင်ခြည်ကြောင့်ဖြစ်ပေါ်လာသောဆူညံသံများကိုကာကွယ်ပေးနိုင်သည်။ကြေးနီမြေကွက် 2 ခုကို အောက်ခြေအလွှာတွင် ပိုင်းခြားပြီး ဖြတ်၍ ESP32-C ၏ အလယ်အလွှာသို့ စုစည်းထားသည်။RF ပါဝါမြေပြင်သည် signal ground loop ထက်နိမ့်သော impedance လိုအပ်သည်၊ ထို့ကြောင့် လုံလောက်စွာနိမ့်သော impedance ကိုသေချာစေရန် power ground မှ chip pad သို့ 6 ဆင့်ရှိသည်။crystal oscillator ၏ ground loop သည် ၎င်းကိုဖြတ်၍ RF power စီးဆင်းခြင်းမပြုနိုင်ပါ၊ သို့မဟုတ်ပါက crystal oscillator သည် frequency jitter ထုတ်ပေးမည်ဖြစ်ပြီး WiFi frequency offset သည် data ပေးပို့လက်ခံနိုင်မည်မဟုတ်ပေ။

7. နောက်ခံမီး LED ပါဝါထောက်ပံ့မှု ဆားကစ်- SOT23-6LED ဒရိုက်ဘာ ချစ်ပ်ပြားနမူနာ။LED သို့ DC/DC ပါဝါထောက်ပံ့မှုသည် အမှီအခိုကင်းစွာဖြင့် ကွင်းဆက်ပုံစံဖြစ်ပြီး DC/DC မြေပြင်သည် 3.3V LOD မြေပြင်နှင့် ချိတ်ဆက်ထားသည်။PWM2 port core ကို အထူးပြုထားသောကြောင့်၊ ၎င်းသည် 600K PWM signal ကိုထုတ်ပေးပြီး PWM output ကို ON/OFF ထိန်းချုပ်မှုအဖြစ်အသုံးပြုရန်အတွက် RC တစ်ခုထပ်ထည့်ထားသည်။

8. ဗို့အားအဝင်အကွာအဝေး- DC/DC အဆင့်နှစ်ဆင့်ချခြင်းကို ဒီဇိုင်းထုတ်ထားသည်။DC/DC circuit ရှိ R13 နှင့် R17 resistors များကို ချန်လှပ်၍မရကြောင်း သတိပြုပါ။DC/DC ချစ်ပ်နှစ်ခုသည် ပြင်ပပါဝါထောက်ပံ့မှုအတွက် အဆင်ပြေသည့် 18V input အထိ ထောက်ပံ့ပေးသည်။

9. USB TYPE C အမှားရှာအပေါက်- TYPE C ကို ပလပ်တပ်နိုင်ပြီး ရှေ့နှင့်နောက်သို့ ပလပ်ဖြုတ်နိုင်သည်။ထပ်ဆင့်ထည့်သွင်းခြင်းသည် WIFI ချစ်ပ် ESP32-C နှင့် ဆက်သွယ်ပေးပါသည်။ပြောင်းပြန်ထည့်သွင်းခြင်းသည် T5L ကို အစီအစဉ်ဆွဲရန် XR21V1410IL16 နှင့် ဆက်သွယ်သည်။TYPE C သည် 5V ပါဝါထောက်ပံ့မှုကို ပံ့ပိုးပေးသည်။

10. Parallel port ဆက်သွယ်မှု- T5L OS core တွင် အခမဲ့ IO port အများအပြားရှိပြီး 16bit parallel port communication ကို ဒီဇိုင်းထုတ်နိုင်သည်။ST ARM FMC parallel port protocol နှင့် ပေါင်းစပ်ထားပြီး၊ ၎င်းသည် synchronous read and write ကို ပံ့ပိုးပေးပါသည်။

11. LCM RGB မြန်နှုန်းမြင့် အင်တာဖေ့စ်ဒီဇိုင်း- T5L RGB အထွက်အား LCM RGB နှင့် တိုက်ရိုက်ချိတ်ဆက်ထားပြီး LCM ရေလှိုင်းအနှောင့်အယှက်များကို လျှော့ချရန်အတွက် ကြားခံခံနိုင်ရည်အား အလယ်တွင် ထည့်သွင်းထားသည်။ဝိုင်ယာကြိုးတပ်သည့်အခါ၊ အထူးသဖြင့် PCLK အချက်ပြမှု RGB အင်တာဖေ့စ်ချိတ်ဆက်မှု၏ အရှည်ကို လျှော့ချပြီး RGB အင်တာဖေ့စ် PCLK၊ HS၊ VS၊ DE စမ်းသပ်မှုအမှတ်များကို တိုးမြှင့်ပါ။စခရင်၏ SPI ပေါက်ကို T5L ၏ P2.4~P2.7 အပေါက်များနှင့် ချိတ်ဆက်ထားပြီး၊ မျက်နှာပြင်ဒရိုက်ဘာကို ဒီဇိုင်းထုတ်ရန် အဆင်ပြေသည်။အရင်းခံဆော့ဖ်ဝဲလ်၏ဖွံ့ဖြိုးတိုးတက်မှုကို လွယ်ကူချောမွေ့စေရန် RST၊ nCS၊ SDA၊ SCI စာမေးပွဲအမှတ်များကို လမ်းညွှန်ပါ။

(2) DGUS ကြားခံ

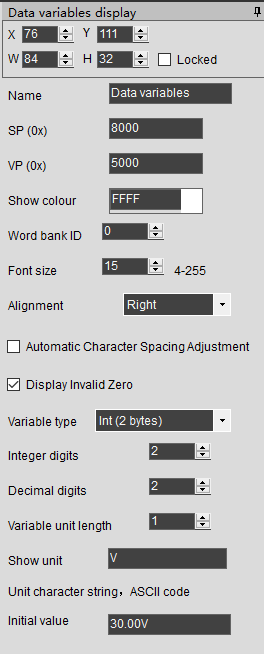

1.6 ဒေတာပြောင်းလဲနိုင်သော display ထိန်းချုပ်မှု

(၃) OS

//———————————— DGUS ဖတ်ရှုရေး ဖော်မတ်

typedef struct

{

u16 addr;//UI 16bit variable လိပ်စာ

u8 datLen;//8bitdata အရှည်

u8 *pBuf;//8bit data pointer

} UI_packTypeDef;//DGUS သည် အစုံလိုက်ဖတ်ပြီး ရေးသည်။

//——————————- ဒေတာပြောင်းလဲနိုင်သော display ထိန်းချုပ်မှု

typedef struct

{

u16 VP;

u16 X;

u16 Y;

u16 အရောင်၊

u8 Lib_ID;

u8 ဖောင့်အရွယ်အစား;

u8 Algnment;

u8 IntNum;

u8 DecNum;

u8 အမျိုးအစား;

u8 LenUint;

u8 StringUinit[11];

} number_spTypeDef;//data variable ဖော်ပြချက် ဖွဲ့စည်းပုံ

typedef struct

{

Number_spTypeDef sp;// SP ဖော်ပြချက် ညွှန်ပြချက်ကို သတ်မှတ်ပါ။

UI_packTypeDef spPack;// SP variable DGUS read and write package ကို သတ်မှတ်ပါ။

UI_packTypeDef vpPack;//define vp variable DGUS read and write package

} Number_HandleTypeDef;//data variable ဖွဲ့စည်းပုံ

ယခင် data variable ဖြင့် handle အဓိပ္ပါယ်။ထို့နောက်၊ ဗို့အားနမူနာပြသမှုအတွက် variable ကိုသတ်မှတ်ပါ-

Number_HandleTypeDef Hsample;

u16 voltage_sample;

ပထမဦးစွာ ကနဦးလုပ်ဆောင်မှုလုပ်ဆောင်ချက်ကို လုပ်ဆောင်ပါ။

နံပါတ်SP_Init(&နမူနာ၊ ဗို့အား_နမူနာ၊ 0×8000);//0×8000 ဤတွင် ဖော်ပြချက် ညွှန်ပြချက် ဖြစ်ပါသည်။

//——Data variable SP pointer တည်ဆောက်ပုံ အစပြုခြင်း—

ပျက်ပြယ်သော NumberSP_Init(Number_HandleTypeDef *number၊u8*value၊ u16 numberAddr)

{

နံပါတ်->spPack.addr = နံပါတ်ထည့်ပါ။

နံပါတ်->spPack.datLen = sizeof(number->sp);

နံပါတ်->spPack.pBuf = (u8 *)&number->sp;

Read_Dgus(&number->spPack);

နံပါတ်->vpPack.addr = နံပါတ်->sp.VP;

switch(number->sp.Type) //vp variable ၏ဒေတာအရှည်ကို DGUS interface တွင်ဒီဇိုင်းရေးဆွဲထားသော data variable type အရ အလိုအလျောက်ရွေးချယ်သည်။

{

ဖြစ်ရပ် 0-

အမှုတွဲ ၅-

နံပါတ်->vpPack.datLen = 2;

ချိုး;

အမှုတွဲ 1-

အမှု ၂-

ဖြစ်ရပ် ၃-

အမှုတွဲ ၆-

နံပါတ်->vpPack.datLen = 4;

အမှုတွဲ ၄-

နံပါတ်->vpPack.datLen = 8;

ချိုး;

}

နံပါတ်->vpPack.pBuf = တန်ဖိုး၊

}

စတင်လုပ်ဆောင်ပြီးနောက်၊ Hsample.sp သည် ဗို့အားနမူနာဒေတာကိန်းရှင်၏ ဖော်ပြချက်ညွှန်ပြချက်ဖြစ်သည်။Hsample.spPack သည် DGUS အင်တာဖေ့စ်လုပ်ဆောင်ချက်မှတဆင့် UI ဗို့အားနမူနာဒေတာပြောင်းလဲနိုင်သော ဒေတာကို OS Core နှင့် UI ဗို့အားနမူနာကြားတွင် ဆက်သွယ်ရေးညွှန်ပြချက်ဖြစ်သည်။Hsample.vpPack သည် DGUS အင်တာဖေ့စ်လုပ်ဆောင်ချက်မှတစ်ဆင့် ဖောင့်အရောင်များ စသည်တို့ကဲ့သို့ ဗို့အားနမူနာဒေတာကို ပြောင်းလဲခြင်း၏ ရည်ညွှန်းချက်ဖြစ်သည်။Hsample.vpPack.addr သည် ကနဦးလုပ်ဆောင်မှုလုပ်ဆောင်ချက်မှ အလိုအလျောက်ရရှိထားသော ဗို့အားနမူနာဒေတာ ကိန်းရှင်လိပ်စာဖြစ်သည်။DGUS အင်တာဖေ့စ်ရှိ မပြောင်းလဲနိုင်သော လိပ်စာ သို့မဟုတ် ပြောင်းလဲနိုင်သော ဒေတာအမျိုးအစားကို သင်ပြောင်းလဲသောအခါ၊ OS core ရှိ ပြောင်းလဲနိုင်သောလိပ်စာကို တပြိုင်တည်း အပ်ဒိတ်လုပ်ရန် မလိုအပ်ပါ။OS core သည် voltage_sample variable ကို တွက်ချက်ပြီးနောက်၊ ၎င်းကို အပ်ဒိတ်လုပ်ရန်အတွက် Write_Dgus(&Hsample.vpPack) လုပ်ဆောင်ချက်ကို လုပ်ဆောင်ရန် လိုအပ်ပါသည်။DGUS ဂီယာအတွက် voltage_sample ကိုထုပ်ပိုးရန်မလိုအပ်ပါ။

စာတိုက်အချိန်- ဇွန်-၁၅-၂၀၂၂